This study material has been compiled from a lecture audio transcript and a PDF document, providing a comprehensive overview of digital circuit design with FPGAs.

📚 Digital Circuit Design with FPGAs: A Study Guide

🚀 Introduction to FPGAs and Digital Design Fundamentals

Field-Programmable Gate Arrays (FPGAs) are powerful, reconfigurable integrated circuits that allow designers to implement custom digital logic. Understanding their core components and operational principles is crucial for modern digital design. This guide explores the essential building blocks and design flow that enable FPGAs to offer immense flexibility and power in hardware implementation, from basic logic elements to complex state machines.

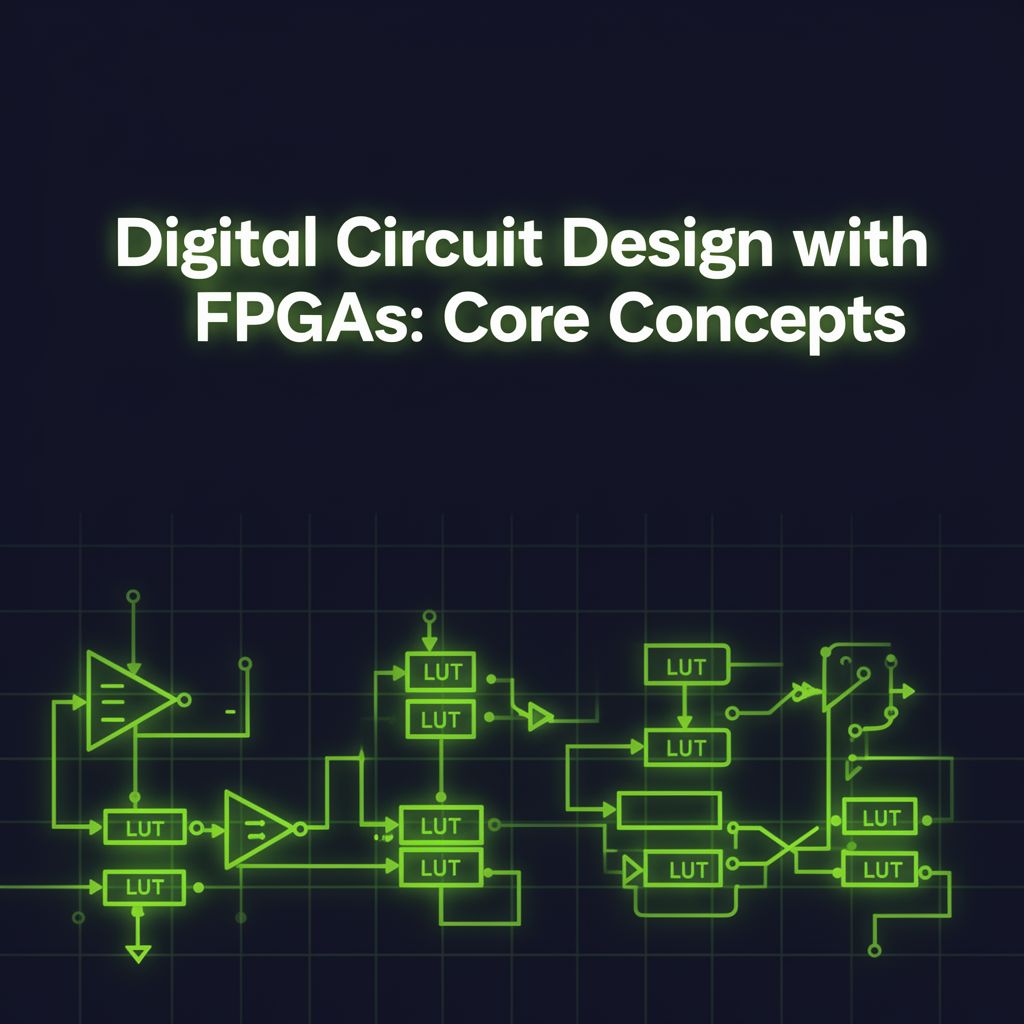

⚙️ Fundamental Logic Elements in FPGAs

At the heart of FPGA functionality are several key logic elements that serve as the basic toolkit for constructing complex digital logic.

1️⃣ Look-Up Table (LUT)

📚 Definition: A Look-Up Table (LUT) is a fundamental component in FPGAs, essentially acting as a truth table. ✅ Functionality: * It defines the output for every possible combination of its inputs. * In an FPGA, a LUT shows the specific inputs and outputs for the logic it implements. * Commonly, FPGAs use 4-input LUTs. ✅ Output Types: * Combinational: The output changes immediately with its inputs. * Synchronized: The output is stable and timed, often with a clock signal. 💡 Insight: LUTs are highly flexible, capable of implementing any Boolean function up to their input capacity.

2️⃣ 1-bit Register (Flip-Flop)

📚 Definition: A 1-bit Register, often implemented as a Flip-Flop, is a sequential logic element. ✅ Functionality: * It is vital for storing state information. * Allows digital circuits to "remember" past inputs or conditions. * Fundamental for sequential logic, where the output depends not only on current inputs but also on past inputs.

3️⃣ Multiplexers (Muxes)

📚 Definition: Multiplexers are data selectors. ✅ Functionality: * They choose one of several input signals. * They forward the selected input onto a single output line. * Crucial for routing data and selecting specific logic paths within the FPGA.

🏗️ FPGA Architecture and Logic Elements (Example: Cyclone IV)

Let's explore how these fundamental elements are integrated within an FPGA architecture, using the Cyclone IV as an example.

Logic Array Block (LAB)

✅ Structure: A Logic Array Block (LAB) is a larger organizational unit within an FPGA. * In a Cyclone IV device, a LAB typically contains 16 Logic Elements (LEs).

Logic Element (LE)

📚 Definition: A Logic Element (LE) is the smallest configurable unit within an FPGA that can implement a piece of logic.

✅ Configuration:

* The configuration data defining the function of LEs and their interconnections is held in Static Random-Access Memory (SRAM) within the FPGA.

* This SRAM is loaded during the FPGA's power-up sequence, making the device "programmable" in the field.

✅ Functionality:

* An LE can be configured to implement two independent 4-input functions, often designated as X and Y.

* Each function typically uses one LE, constrained by area and timing.

* Example: Inputs like data1 and data3 might connect to variables, while data4 could be tied to a constant value like '0'.

* Final multiplexers within the LE select the appropriate LUT outputs to form the desired logic.

✅ Handling Complex Functions:

* For functions with more than four inputs (e.g., x = KLM), the FPGA handles this by:

* Cascading multiple LEs.

* Utilizing specialized routing to break down the larger function into smaller, 4-input segments that individual LUTs can manage.

📊 FPGA Design Flow: From Code to Hardware

The process of designing and implementing a digital circuit on an FPGA follows a structured flow:

- ✍️ Hardware Description Language (HDL) Design:

- The designer writes HDL code (typically VHDL or Verilog).

- This code describes the desired digital circuit's behavior.

- ⚙️ Synthesis:

- The HDL code is translated and mapped onto the specific physical resources of the FPGA.

- This includes mapping logic to LUTs, Flip-Flops (FFs), and routing paths.

- ⬇️ Configuration Data Download:

- Once synthesized, the configuration data is generated.

- This data is then downloaded to the FPGA's internal SRAM.

- 🚀 Hardware Execution:

- The FPGA executes the implemented hardware, performing the functions defined by the designer's code.

🔄 Implementing Sequential Logic and State Machines

FPGAs are highly adept at implementing sequential logic, particularly finite state machines (FSMs).

✅ State Machine Implementation: * Intermediate Functions: One LE (e.g., LE1) might compute an intermediate function. * Chaining Logic: Another LE (e.g., LE2) would then use LE1's output as one of its own inputs, creating a chain of logic for complex state transitions. * Next-State Logic: Typically, two LEs are used to generate the next-state logic. * State Bit Storage: Each LE's integrated flip-flop holds one state bit, preserving the current state until the next clock edge. * Internal Control: Critical control signals (reset, load, enable) are managed by the internal LE control logic, simplifying the design process and ensuring proper synchronization.

➕ Other Relevant Digital Concepts

Beyond the core FPGA components, other digital circuit concepts are important:

- Decoders:

- Function: A decoder takes

ninputs and activates one of2^noutputs based on the binary value of the inputs. - Example: A 2:4 decoder takes two inputs (A, B) and activates one of four outputs.

- Function: A decoder takes

- Programmable Logic Arrays (PLAs):

- Function: PLAs are another type of programmable logic device.

- They are capable of implementing sum-of-products logic forms, offering flexibility in realizing Boolean functions.

- Pseudo-nMOS Circuits: This refers to a specific circuit style, often used in older or specialized digital designs, which falls under the broader umbrella of digital design techniques.

This guide provides a foundational understanding of FPGA architecture, design flow, and key digital logic concepts, essential for anyone studying modern digital hardware implementation.